# SNC8508数据手册

集成高质量Codec、高性能DSP和高速USB的AIoT人机交互音频处理器

# 产品概览

SNC8508是一款集成AI算法和高质量音频编解码器、高性能DSP、高速USB与PMU的专业音频处理器。它具有24位高采样率ADC/DAC,支持2路模拟和10路数字麦克风输入,支持2路模拟差分或立体声音频输出;内建1个Tensilica HiFi3数字信号处理器,可集成多种AI音频算法;支持UAC1.0/2.0音频服务,内建PMU和多种扩展接口,只需添加几个无源组件,即可提供完整的专业音频解决方案,实现高集成度、高性能、低BOM成本的专业产品。配合九音技术开发生态,实现快速产品开发与客户定制。

# 产品特性

# 内核和存储

Cadence® Tensilica® HiFi3 音频DSP,主频高达200MHz

Single-cycle MAC, vector FPU, SIMD

支持JTAG调试追踪

专用硬件加速器

256KB IRAM, 256KB DRAM, 48KB cache RAM

内置1MB NOR Flash

内置一次性烧录存储器可保存关键信息

# 音频接口

2路24位高精度ADC, SNR≥106dB,支持多种采样率: 8, 11.025, 12, 16, 22.05, 24, 32, 44.1, 48, 88.2, 96, 176.4, 192kHz

2路单端或差分模拟输入,可编程控制线路输入或麦克风输入的电容配置,支持两级增益放大输入音频

10路单声道或5路立体声数字麦克风接口,具有可编程DMIC时钟频率

优化SNR的自动增益控制

支持低功耗模式,自动语音检测功能可在低功耗模式下检测到语音活动时唤醒芯片

可编程控制的风噪抑制

2路24位高精度DAC, SNR≥110dB,支持多种采样率: 8, 11.025, 12, 16, 22.05, 24, 32, 44.1, 48, 88.2, 96, 176.4, 192kHz

内置耳机放大器,可直接驱动扬声器

支持音频输出的动态范围控制

2路双工I2S, 采样率支持8K~192KHz, 字长最高32bits

内置USB 2.0 PHY,支持USB音频协议UAC 1.0/2.0

# 音频信号处理

专利近场及远场噪声消除算法

主动回声消除算法

混响消除算法

音频输入/输出EQ处理

波束成形与声源定位

# 低功耗管理与时钟

供电范围:3.3V到5.5V

内置低功耗电压管理模块PMU

内置DC-DC电压转换和LDO电源可提供芯片电路全部所需电压

支持上电复位(POR), 欠压重启(BOR), 过压保护

低功耗睡眠模式,支持始终在线类型的应用

晶振频率:24MHz或26MHz

片上PLL提供芯片全部所需时钟信号

# 外设接口

8 x GPIO口

2 x 双工I2S, 采样率支持8K~192KHz, 字长最高32bits

2 x I2C, 支持主从模式

1 x USB,支持USB音频协议UAC 1.0/2.0

1 x UART(全双工)

2 x 12-bit SAR ADC,可用于耳机按钮检测、电池监视器或其他模拟传感器输入测量

# 应用

远场拾音类应用

AIoT音频应用

特种监听设备

感知类应用

# 功能框图

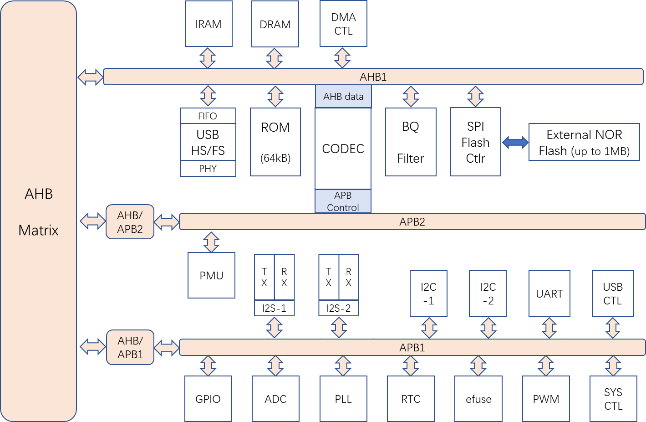

SNC8508结合了高质量音频编解码器,高性能HiFi3 DSP和丰富的外设接口。SNC8508具有片上24位/192kHz采样率ADC/DAC,数字和模拟麦克风接口、麦克风前置放大器和耳机放大器,是真正的单芯片音频解决方案,可实现低功耗的高质量音频应用。

SNC8508集成了一颗高达200MHz的Cadence HiFi3 DSP内核,可用于系统控制和音频数字信号处理;2路高质量24位/192kHz采样率ADC,支持2路模拟麦克风输入和多达10路数字麦克风输入,并内置两级音频输入增益放大;2路高质量24位/192kHz采样率DAC,内置耳机放大器,可直接驱动立体声耳机输出。它提供高达512KB的零等待RAM和大小可配置的闪存(默认为1MB)。片内电源管理单元只需要单独一路电源输入就可以提供所有音频接口的供电,满足片内全部单元的电压要求。它有一个始终在线的模块域,可实现超低功耗待机。它具备丰富的外设接口,包括1个高速USB 2.0 PHY,2个双工I2S,2个I2C,1个UART,高达8个GPIO管脚,还提供了2个12位的辅助ADC,可用于按钮识别、模拟传感器监控等功能。

SNC8508的DSP处理器实现了丰富的音频数字处理功能,包括输入自动增益控制,风噪抑制,回声消除,混响消除,主动降噪,自动语音激活,均衡器,混音器,输出动态范围控制,声源定位等。开发者使用九音SDK可快速实现定制化应用。无论是通过USB、模拟连接还是无线连接,SNC8508都能提供所需的数字处理能力,充分提升音频产品的功能和性能。

# 产品封装

| Part Number | Package | Body Size (NOM) |

|---|---|---|

| SNC8508 | BGA 80 | 4.50mm*6.20mm |

# 引脚配置和功能

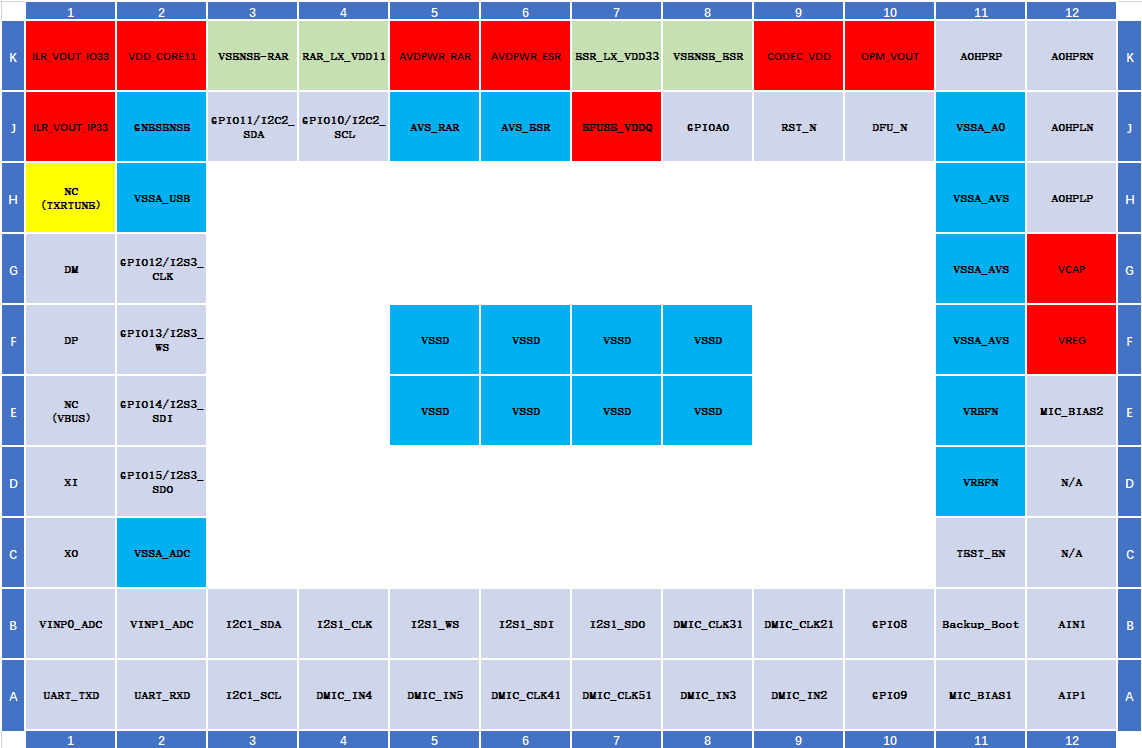

引脚定义和位置列表:

| Function | Pin name | 80 Ball BGA | Type | Description |

|---|---|---|---|---|

| Xtal Oscillator | XI | D1 | Analog | 24MHz crystal port |

| XO | C1 | Analog | 24MHz crystal port | |

| PMU | VDD_IP33 | J1 | Analog | 3.3V for analog block |

| VDD_IO33 | K1 | Analog | 3.3V for IO | |

| CODEC_VDD | K9 | Analog | 3.3V for Codec | |

| AVDPWR_RAR | K5 | Analog | External power supply | |

| AVDPWR_ESR | K6 | Analog | External power supply | |

| OPM_VOUT | K10 | Analog | Protection LDO output | |

| VDD_CORE11 | K2 | Analog | 1.1V for digital core | |

| ESR_LX | K7 | Analog | DCDC2 switch pin | |

| VSENSE_ESR | K8 | Analog | DCDC2 sense pin | |

| RAR_LX | K4 | Analog | DCDC1 switch pin | |

| VSENSE-RAR | K3 | Analog | DCDC1 sense pin | |

| EFUSE_VDDQ | J7 | Analog | Supply for eFuse | |

| Digital Interface | I2C_CLK | A3 | I/O | I2C interface clock |

| I2C_DAT | B3 | I/O | I2C interface data | |

| GPIO0 | B4 | I/O | I2S1_clk | |

| GPIO1 | B5 | I/O | I2s1_ws | |

| GPIO2 | B6 | I/O | I2s1_sdi | |

| GPIO3 | B7 | I/O | I2s1_sdo | |

| GPIO4 | A4 | I/O | I2s2_clk | |

| GPIO5 | A5 | I/O | I2s2_ws | |

| GPIO6 | A6 | I/O | I2s2_sdi | |

| GPIO7 | A7 | I/O | I2s2_sdo | |

| DMIC_IN1 | A10 | I | DMIC1/2 input (GPIO9) | |

| DMIC_IN2 | A9 | I | DMIC3/4 input | |

| DMIC_IN3 | A8 | I | DMIC5/6 input | |

| DMIC_CLK11 | B10 | O | DMIC1/2 clock (GPIO8) | |

| DMIC_CLK21 | B9 | O | DMIC3/4 clock | |

| DMIC_CLK31 | B8 | O | DMIC5/6 clock | |

| RST_N | J9 | I | Chip reset | |

| GPIOAO | J8 | I | Always-on wake up | |

| UART_TXD | A1 | O | UART TX data | |

| UART_RXD | A2 | I | UART RX data | |

| DFU_N | J10 | I | Firmware update enable | |

| Backup_Boot | B11 | I | For backup boot vector | |

| GPIO10 | J4 | I/O | ||

| GPIO11 | J3 | I/O | ||

| GPIO12 | G2 | I/O | ||

| GPIO13 | F2 | I/O | ||

| GPIO14 | E2 | I/O | ||

| GPIO15 | D2 | I/O | ||

| TEST-EN | C11 | I/O | ||

| Audio Interface | VREG | F12 | Analog | Audio supply |

| VCAP | G12 | Analog | Audio biasing De-cap | |

| AIP1 | A12 | Analog | MIC1 input P port | |

| AIN1 | B12 | Analog | MIC1 input N port | |

| AIP2 | D12 | Analog | MIC2 input N port | |

| AIN2 | C12 | Analog | MIC2 input P port | |

| MICBIAS1 | A11 | Analog | Micbias 1 | |

| MICBIAS2 | E12 | Analog | Micbias 2 | |

| AOHPLP | H12 | Analog | Left DAC P port | |

| AOHPLN | J12 | Analog | Left DAC N port | |

| AOHPRN | K12 | Analog | Right DAC N port | |

| AOHPRP | K11 | Analog | Right DAC P port | |

| Auxiliary ADC | VINP0_ADC | B1 | Analog | GPADC0 input |

| VINP1_ADC | B2 | Analog | GPADC1 input | |

| USB | NC(TXRTUNE) | H1 | Analog | NC or (USB tuning) |

| DM | G1 | Analog | USB DP | |

| DP | F1 | Analog | USB DM | |

| NC(VBUS) | E1 | Analog | NC or (VBUS detection) | |

| GND | VSSA_ADC | C2 | Analog | Analog GND |

| VSSA_USB | H2 | Analog | Analog GND | |

| VSSD | F5678,E5678 | Analog | Digital GND | |

| VSSA_AVS | H11,G11,F11 | Analog | Codec analog GND | |

| AVS_ESR | J6 | Analog | DCDC2 GND | |

| AVS_RAR | J5 | Analog | DCDC1 GND | |

| GNDSENSE | J2 | Analog | All regulator GNDsenses | |

| VSSA_A0 | J11 | Analog | DAC driver GND | |

| VREFN | E11,D11 | Analog | Codec reference GND |

# 产品规格

# 绝对最大额定值

| Parameter | Symbol | Min. | Max. | Unit |

|---|---|---|---|---|

| Power | AVDPWR | -0.3 | 5.5 | V |

| AVDD | -0.3 | 3.63 | V | |

| VDD_IP33 | -0.3 | 3.63 | V | |

| VDD_IO33 | -0.3 | 3.63 | V | |

| VDD_OPM | -0.3 | 3.63 | V | |

| VDD_eFuse | -0.3 | 2.75 | V |

# 工作环境要求

| Parameter | Symbol | Min | Max | Unit |

|---|---|---|---|---|

| Ambient Temperature | Ta | -20 | 80 | °C |

| ESD | HBM | -2000 | 2000 | V |

| CMD | -500 | 500 | V |

# 建议工作条件

| Parameter | Test condition | Min. | Typ. | Max. | Unit | |

|---|---|---|---|---|---|---|

| AVDPWR | Power Supply Voltage range | Referenced to VSS | 3.3 | 5 | 5.5 | V |

| AVDD | Referenced to AVSS | 3.2 | 3.3 | 3.4 | ||

| VDD_IP33 | Referenced to AVSS | 3.2 | 3.3 | 3.4 | ||

| VDD_IO33 | Referenced to IOVSS | 3.2 | 3.3 | 3.4 | ||

| DVDD | Referenced to DVSS | 1.05 | 1.1 | 1.15 | ||

| Main Clock | - | 12 | 13 | MHz | ||

| I2C SCL Clock Frequency | Full Speed | - | 100 | 400 | KHz | |

| Analog input maximum signal range | Full Scale, Gain GID* = 0 dB, boost gain GIM* = 0 dB | 0 | 0.53 | 2.12 | Vpeak | |

| Output load resistace (Rl) | Differential configuration | 16 | Ω | |||

| Output load capacitance | 200 | pF | ||||

| Operating Temperature | -20 | 80 | °C | |||

# 音频ADC输入特性

| Condition: - 40°C to +100°C, AVDD=3.3Vm DVDD=1.1V. Input sine wave with a frequency of 1 kHz, measurement bandwidth 20 Hz - Fs/2 for Fs < 48 kHz, measurement bandwidth 20 Hz - 20 kHz for Fs = 48 kHz to 192 kHz, normal mode, capacitor-less input configuration, unless otherwise specified. | |||||

| Parameter | Test condition | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Input level | Full Scale, Gain GID* = 0 dB, boost gain GIM* = 0 dB | 2.12 | Vpp | ||

| Full Scale, Gain GID* = 0 dB, boost gain GIM* = 20 dB | 0.212 | Vpp | |||

| THD+N | 1 kHz sine wave @ Full Scale -3 dB and gain GID* = 0 dB, boost gain GIM* = 0 dB, normal mode and low power mode | 88 | dB | ||

| Dynamic Range | A-weighted, 1 kHz sine wave, normal mode | 106.5 | dB | ||

| A-weighted, 1 kHz sine wave, low power mode | 103.5 | dB | |||

| SNR | A-weighted, 1 kHz sine wave, with activation of the SNR optimizer feature | 106 | dB | ||

| A-weighted, 1 kHz sine wave, gain GID* = 0 dB, boost gain GIM* = 0 dB, normal mode | 94.5 | dB | |||

| A-weighted, 1 kHz sine wave, gain GID* = 0 dB, boost gain GIM* = 0 dB, low power mode | 90.5 | dB | |||

| PSRR | 100 mVpp 1 kHz sinewave is applied to AVD, input data is 0 and gain GID* = 0 dB, boost gain GIM* = 0 dB | 90 | dB | ||

| Input referred noise | A-weighted, 1 kHz sine wave @ Full Scale and gain GID* = 0 dB, boost gain GIM* = 20 dB, normal mode | 3.6 | uVrms | ||

| A-weighted, 1 kHz sine wave @ Full Scale and gain GID* = 0 dB, boost gain GIM* = 20 dB, low power mode | 5 | uVrms | |||

| Channel separation | 1 kHz sine wave @ Full Scale on one channel, no signal on the other channel and gain GID* = 0 dB, boost gain GIM* = 0 dB | 108 | dB | ||

| Inter-channel phase mismatch | 1 kHz sine wave @ Full Scale on two channels and gain GID* = 0 dB, boost gain GIM* = 0 dB, input bypass capacitor inter-channel mismatch = 10% max, master mode | 0.1 | ° | ||

| Gain range | Boost gain GIM* when activated | -2 | 24 | dB | |

| Digital gain GID* | -64 | 63 | dB | ||

| Gain step | GIM* @1kHz | 2 | dB | ||

| GID* @1kHz | 1 | dB | |||

| Gain accuracy | GIM* @1kHz | -1 | 1 | dB | |

| GID* @1kHz | -0.5 | 0.5 | dB | ||

| Input impedance (differential configuration) | Boost gain GIM* = 20 dB Includes 10 pF for ESD, bonding and package pins capacitances | 20 | pF | ||

| Input impedance (single-ended configuration) | Boost gain GIM* = 20 dB Includes 10 pF for ESD, bonding and package pins capacitances | 20 | pF | ||

| Polarity | AIP*-AIN* to DIL/R | 1 | |||

# 音频DAC输出特性

| Condition: - 40°C to +80°C, AVDD=3.3Vm DVDD=1.1V. Input sinewave with a frequency of 1kHz, measurement bandwidth 20Hz-20kHz, unless otherwise specified. | |||||

| Parameter | Test condition | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Output level | Full Scale, gain GOL/R = +6 dB, GODL/R = 0 dB, 10 kOhms load | 5.6 | Vpp | ||

| Full Scale, gain GOL/R = +5 dB, GODL/R = 0 dB, 128 Ohms load | 4.99 | Vpp | |||

| Full Scale, gain GOL/R = +3 dB, GODL/R = 0 dB, 32 Ohms load | 3.96 | Vpp | |||

| Full Scale, gain GOL/R = 0 dB, GODL/R = 0 dB, 16 Ohms load | 2.8 | Vpp | |||

| Output power | 200 Ohms load | 19.6 | mW | ||

| 16 Ohms load | 60 | mW | |||

| SNR | A-weighted, 1 kHz sine wave @ Full Scale, gain GOL/R = +6 dB, GODL/R = 0 dB, 10 kOhms load | 110 | dB | ||

| Dynamic Range | A-weighted, 1 kHz sine wave @ Full Scale, gain GOL/R = [-10 +6] dB, GODL/R = 0 dB, 10 kOhms load | 110 | dB | ||

| Idle Noise | A-weighted with no signal, gain GOL/R=-10dB, GODL/R = 0 dB, 10k Ohms load | -104.9 | dBV | ||

| THD+N | 1 kHz sine wave @ Full Scale -1 dB, gain GOL/R = +6 dB, GODL/R = 0 dB, 10 kOhms load | 87 | dB | ||

| 1 kHz sine wave @ Full Scale -1 dB, gain GOL/R = +5 dB, GODL/R = 0 dB, 128 Ohms load | 85 | dB | |||

| 1 kHz sine wave @ Full Scale -1 dB, gain GOL/R = 0 dB, GODL/R = 0 dB, 16 Ohms load | 79 | dB | |||

| PSRR | 100 mVpp 1 kHz is applied to AVD, input data is 0 and gain GOL/R = 0 dB, GODL/R = 0 dB, 10 kOhms load capacitor inter-channel mismatch = 10% max, master mode | 90 | dB | ||

| 100 mVpp 1kHz is applied to VDDAO, input data is 0 and gain GOL/R = 0 dB, GODL/R = 0 dB, 10 kOhms load | 70 | dB | |||

| Analog gain | Gain GOL/R | -19 | 12 | dB | |

| Digital gain | Gain GODL/R | -31 | 32 | dB | |

| Gain step | GOL/R, GODL/R @1 kHz | 1 | dB | ||

| Gain accuracy | GOL/R, GODL/R @1 kHz | -0.5 | 0.5 | dB | |

| Pop-up Noise | Active <-> Inactive, 10 kOhms load | -60 | dBV | ||

| Active <-> Inactive, 16 Ohms load | -60 | dBV | |||

| Output load resistance (Rl) | 32 | ohms | |||

| Output load capacitance (Cp) | 200 | pF | |||

# 模拟麦克风接口特性

| Condition: - 20°C to +80°C, AVDD=3.3Vm DVDD=1.1V. Input sine wave with a frequency of 1 kHz, measurement bandwidth 20 Hz - Fs/2 for Fs \< 48 kHz, measurement bandwidth 20 Hz - 20 kHz for Fs = 48 kHz to 192 kHz, normal mode | |||||

| Parameter | Test conditions | Min. | Typ | Max. | Unit |

|---|---|---|---|---|---|

| Micbias ouput level | 2.5 | V | |||

| Micbias output current Current per MICBIAS output | 2 | mA | |||

| Micbias output current Total current for all MICBIAS outputs | 4 | mA | |||

| VREG output level | 2.35 | 2.5 | 2.65 | V | |

| VCAP output level | 1.9 | 2 | 2.1 | V | |

# 数字麦克风接口特性

| Condition: Input sine wave with a frequency of 1 kHz, MCLK = 12 MHz or 13 MHz, DMIC_CLK = Fmclk/4, measurement bandwidth 20 Hz - Fs/2 for Fs = 8 to 32 kHz, measurement bandwidth 20 Hz - 20 kHz for Fs = 44.1 kHz to 192 kHz, unless otherwise specified. | |||||

| Parameter | Test condition | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Input level | Full Scale max value, Gain GID* = 0 dB | 85.6 | % | ||

| Full Scale min value, Gain GID* = 0 dB | 14.4 | % | |||

| SNR | A-weighted,1kHz sinewave @Full Scale and gain GIDL, GIDR = 0 dB | 100 | dB | ||

| Dynamic Range | A-weighted, 1 kHz sine wave @ Full Scale -60 dB and gain GID* = 0 dB | 100 | dB | ||

| THD+N | 1kHz sinewave @Full Scale-1dB and gain GIDL, GIDR = 0 dB | 90 | dB | ||

| Digital gain | Gain GID* when activated | -64 | 63 | dB | |

| Gain step | GID* @1 kHz | 1 | dB | ||

| Gain accuracy | GID* @1 kHz | -0.25 | 1 | 0.25 | dB |

# 数字麦克风语音检测

| Parameter | Test condition | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Detection Latency | Detection results based on MIWOK≠CTM r1.0, Far-Field configuration, Power Level Sensitivity set to 5 dB, within 60% truncation of the first phoneme | 25.7 | ms | ||

| VDV (Voice Detected as Voice) | 93.5 | % | |||

| NDV (Noise Detected as Voice) | 7 | % | |||

| VTE (Voice Trigger Efficiency) | 93.25 | % | |||

| Detection Latency | Detection results based on MIWOK≠CTM r1.0, Far-Field configuration, Power Level Sensitivity set to 5 dB, within 60% truncation of the first phoneme | 25.7 | ms | ||

| VDV (Voice Detected as Voice) | 98.5 | % | |||

| NDV (Noise Detected as Voice) | 7 | % | |||

| VTE (Voice Trigger Efficiency) | 95.75 | % | |||

| VDV (Voice Detected as Voice) | Detection results based on MIWOK≠CTM r1.0, Far-Field configuration, Power Level Sensitivity set to 5 dB, within the word length | 100 | % | ||

| Minimum Absolute Detection Threshold | -80 | dBFS | |||

| Power Level Sensitivity | 0 | 31 | dB | ||

| Power Level Sensitivity programmable step | 1 | dB |

# LDO特性

| Parameter | Test condition | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Operating Temperrature | Junction temperature | -40 | 100 | °C | |

| Input voltage Range, VAVDPWR | 2.7 | 5.5 | V | ||

| Output voltage | 3.3 | V | |||

| Output voltage Accuracy | ±3 | % | |||

| Maximum Output Current,IMAX | 100 | mA | |||

| Dropout voltage,VDROPOUT | IOUT =IMAX | 380 | mV | ||

| PSRR(Power Supply Rejection Ratio) | @ DC | -45 | -30 | dB | |

| no-load current | ILOAD= 0 mA | 40 | uA |

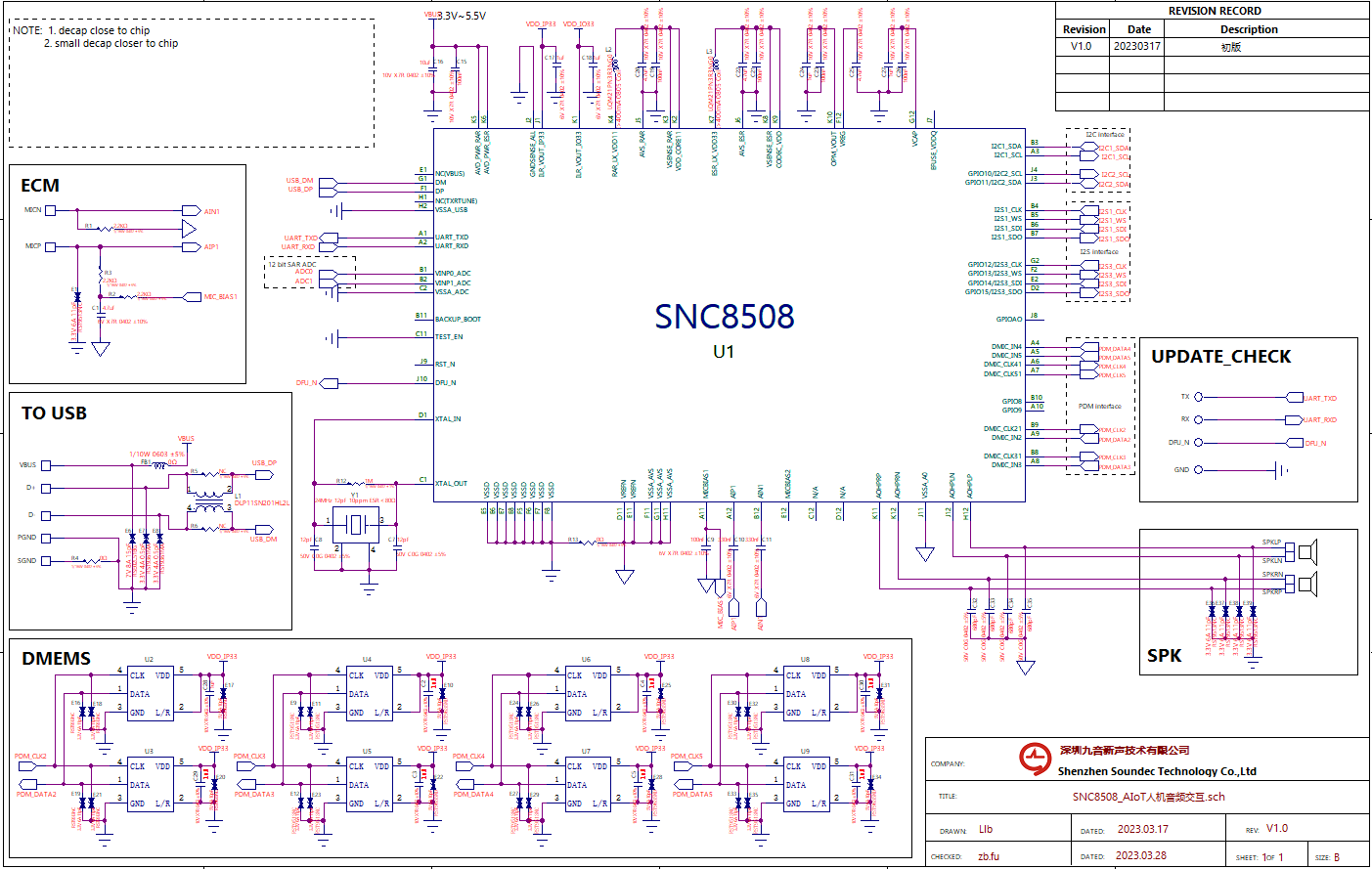

# 系统参考电路

# 工作原理

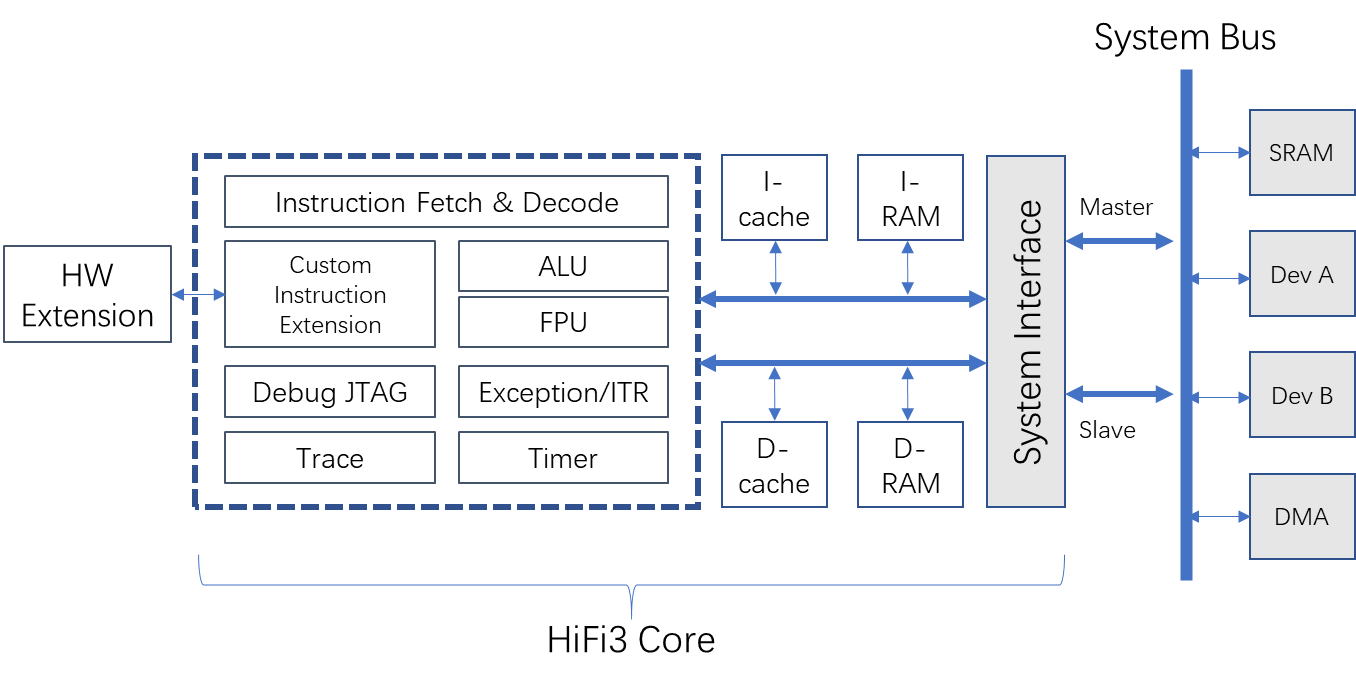

# DSP核心

强大的 Cadence HiFi3 内核可处理系统控制和音频数字信号处理。下图显示了HiFi3架构。

HiFi3核心的主要功能和配置如下表所示:

| Item | Specification | Comment |

|---|---|---|

| Core | Cadence HiFi3 | |

| 32 bit instruction | As system controller and audio signal processing | |

| Processor Clock | Up to 200 MHz | |

| MAC | Single-cycle MAC | |

| FPU | Vector FPU, half-precision | |

| SIMD | Full type of operation | |

| MIPS | 600 MIPS max | 3 slots in HiFi3 |

| I-RAM | 256KB | Local zero-wait RAM for instruction |

| D-RAM | 256KB | Local zero-wait RAM for data |

| I-Cache | 16 KB | 4 cache way, 64 Byte cache line |

| D-Cache | 32 KB | 4 cache way, 64 Byte cache line |

| Bus protocol | AHB-lite | 32-bit data width |

| Timer | 3 timers |

# 中断说明

HiFi3支持32个中断。下表中按优先级列出了这些中断,其中级别数字越高意味着优先级越高。

| Configurable IRQ Num | Function | Interrupt (default) | Priority | Comments |

|---|---|---|---|---|

| 0 | USB IRQ | USB | 4 | |

| 1 | USBDMA | 4 | ||

| 2 | ADC | CODEC_IRQADC12 | 4 | ADC DMIC1/2 or AMIC1/2 interrupt |

| 3 | CODEC_IRQADC34 | 4 | ADC DMIC3/4 interrupt | |

| 4 | CODEC_IRQADC56 | 4 | ADC DMIC5/6 interrupt | |

| 5 | CODEC_IRQADC78 | 4 | ADC DMIC7/8 interrupt | |

| 6 | CODEC_IRQADC9A | 4 | ADC DMIC9/A interrupt | |

| 7 | DAC | CODEC_IRQDAC | 4 | DAC interrupt |

| 8 | SW interrupt_0 | SOFTWARE_INT_0 | 4 | SW interrupt 0 |

| 9 | I2S-1 | I2S-1 IRQ | 4 | I2S-1 word clock interrupt |

| 10 | I2S-2 | I2S-2 IRQ | 4 | I2S-2 word clock interrupt |

| 11 | I2S-3 | I2S-3 IRQ | 4 | I2S-3 word clock interrupt |

| 12 | DMAC | DMAC-IRQ | 4 | DMAC interrupt |

| 13 | Maestro (PMU) | Maestro-IRQ | 4 | Maestro interrupt |

| 14 | Codec | Codec-IRQ | 4 | Codec interrupt on AIAS lock event and headphone output short-circuit detection |

| 15 | Codec-IRQ-WT | 4 | Codec interrupt for VAD | |

| 16 | I2C-1 | I2C-1 IRQ | 3 | I2C-1 IRQ |

| 17 | I2C-2 | I2C-2 IRQ | 3 | I2C-2 IRQ |

| 18 | UART | UART IRQ | 3 | |

| Timer | Timer0-IRQ | 3 | Hifi3 own timer | |

| 19 | GPIO678 | GPIO6-IRQ | 3 | Group to one IRQ |

| GPIO7-IRQ | 3 | |||

| GPIO8-IRQ | 3 | |||

| 20 | RTC | RTC-IRQ | 2 | RTC interrupt |

| 21 | Watchdog | Watchdog-IRQ | 2 | watchdog interrupt (32KHz) |

| 22 | GPIO9ABCDEF | GPIO9-IRQ | 2 | Group to one IRQ |

| GPIO10-IRQ | 2 | |||

| GPIO11-IRQ | 2 | |||

| GPIO12-IRQ | 2 | |||

| GPIO13-IRQ | 2 | |||

| GPIO14-IRQ | 2 | |||

| GPIO15-IRQ | 2 | |||

| 23 | USB_Sleep | USB_Sleep_IRQ | 1 | USB skep mode |

| DSP SW interrupt | DSP_SW_IRQ | 1 | Software IRQ from HiFi3 | |

| Timer | Timer1-IRQ | 1 | Hii3 own timer | |

| Trmer2-IRQ | 1 | Hifi3 own timer | ||

| 24 | ADC | ADC-IRQ | 1 | ADC IRQ with eoc signal |

| 25 | PWM Interrupt | PWM_IRQ | 1 | PWM Interrupt |

| 26 | SW interrupt_1 | SOFTWARE_INT_1 | 1 | SW interrupt 1 |

| Profiling | Profing_IRQ | 1 | Profing interrupt |

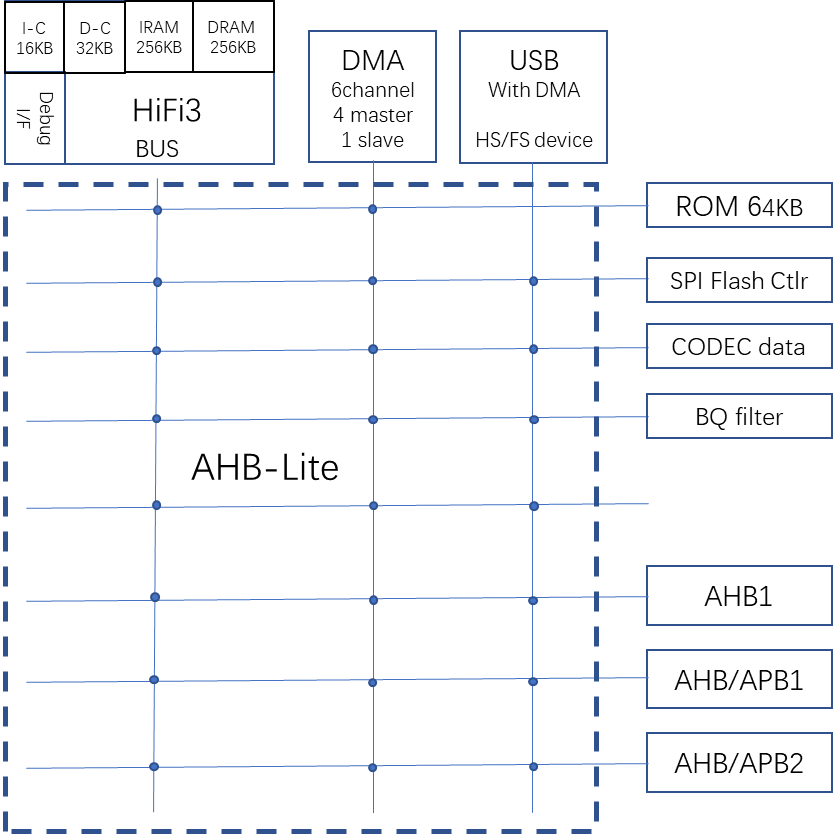

# 系统总线结构

下图显示了多层总线矩阵,其中HiFi3、DMA和USB HS是主机,ROM、SPI闪存控制器、编解码器数据、BQ滤波器和外设是从设备。IRAM和DRAM是TCM型SRAM,具有1个周期的操作。64KB ROM 用于系统引导。硬件 BQ 滤波器连接到 AHB 总线上。

AHB与AHP外设:

# 数据处理流程

有两种典型的数据流案例。下图显示了HiFi3内核的USB音频数据流。左图是USB Type-C耳机的应用案例。右图显示了HiFi3内核的I2S数据流。这是蓝牙耳机、波束成形语音命令产品的应用案例。

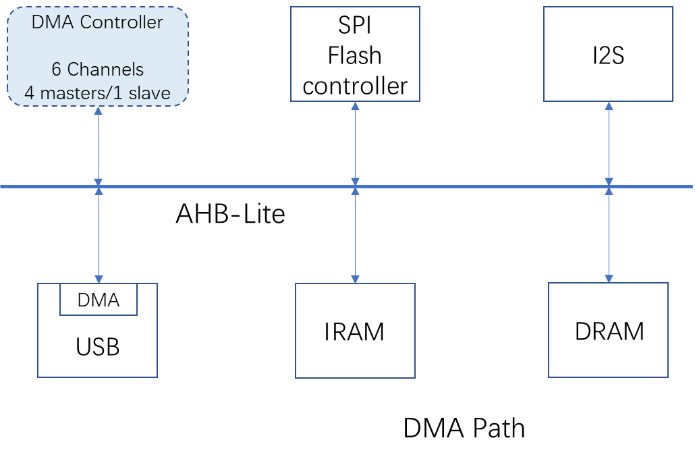

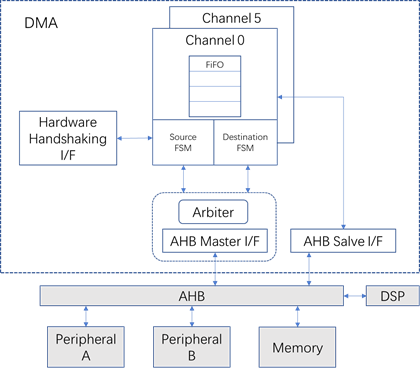

# DMA

DMA控制器连接到AHB总线。数据通过DMA控制器在RAM、闪存控制器和I2S之间传输。USB控制器具有主模式DMA,用于控制DRAM和USB FIFO之间的数据传输。下图显示了DMA的功能执行流程。

DMA 是一个 AHB 中央 DMA 控制器内核,它通过一条或多条 AHB 总线将数据从源外设传输到目标外设,其中包括:

DMA 硬件请求接口

多达6个通道

每个通道的源和目标的FIFO

仲裁器

AHB主接口

AHB从接口

下图显示了DMA框图.

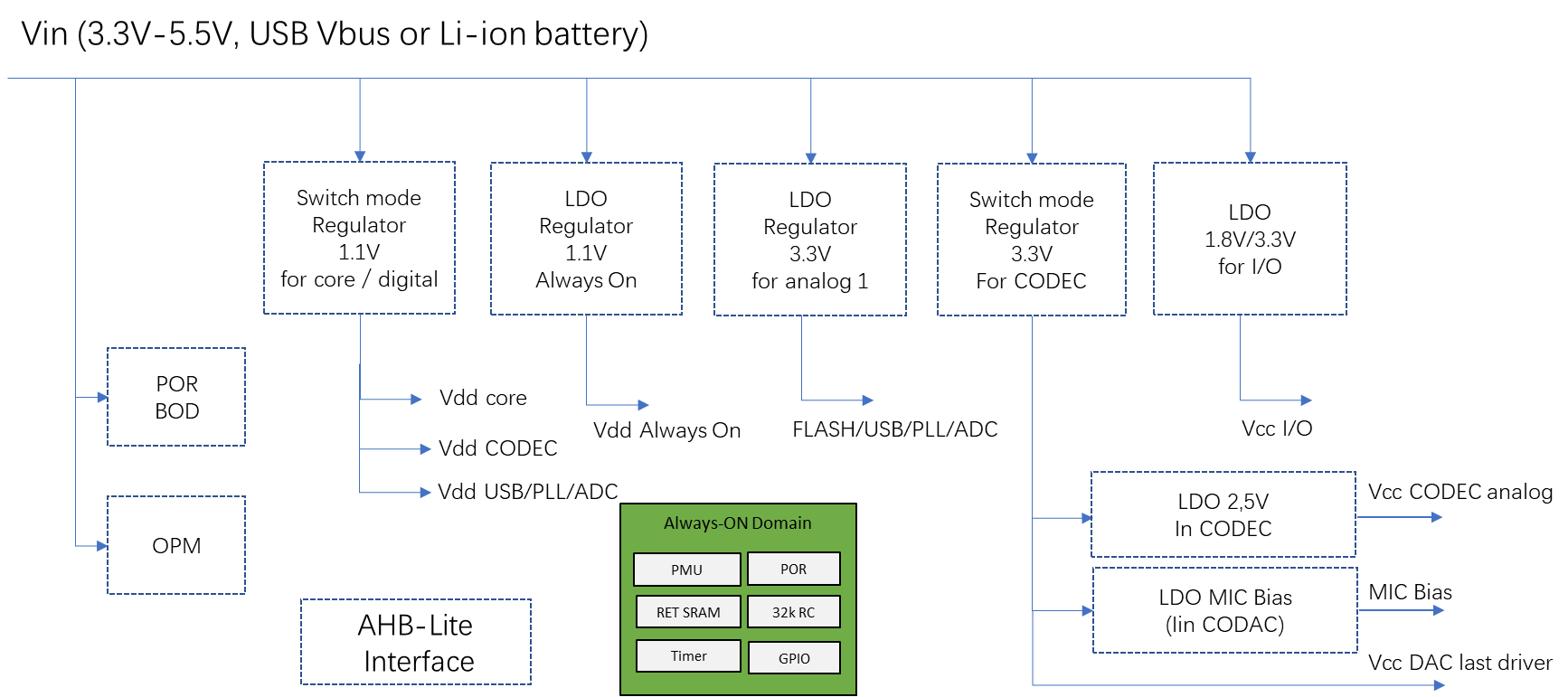

# 启动、初始化和电源管理

芯片供电可用来自USB主机设备 VBUS 或锂离子电池。片上电源管理单元(PMU)以低功耗为所有功能块提供所有必要的电源电压。 编解码器模块可为外部麦克风提供MIC偏置,为音频模拟输出提供2.5V LDO。PMU 支持上电复位 (POR)、掉电检测 (BOD) 和 OVP/OCP/ULP 保护。PMU 可通过 APB 总线设置为在活动模式、睡眠模式和掉电模式下工作。

下图显示了电源体系结构,包括:

3.3V至5.5V单电源输入

1个用于内核和数字的 DC-DC 稳压器:1.1V

1个用于睡眠模式的始终打开的超低功耗LDO:1.1V

1个用于编解码器模拟部分的 DC-DC 稳压器:3.3V

1个 LDO,提供用于其他模拟器件的3.3V电源

1个 LDO,提供用于数字 IO 的3.3V电源

# 上电顺序

启动顺序如下图所述。POR发出复位信号,Maestro将所有稳压器设置到正确的状态。

# 复位网络

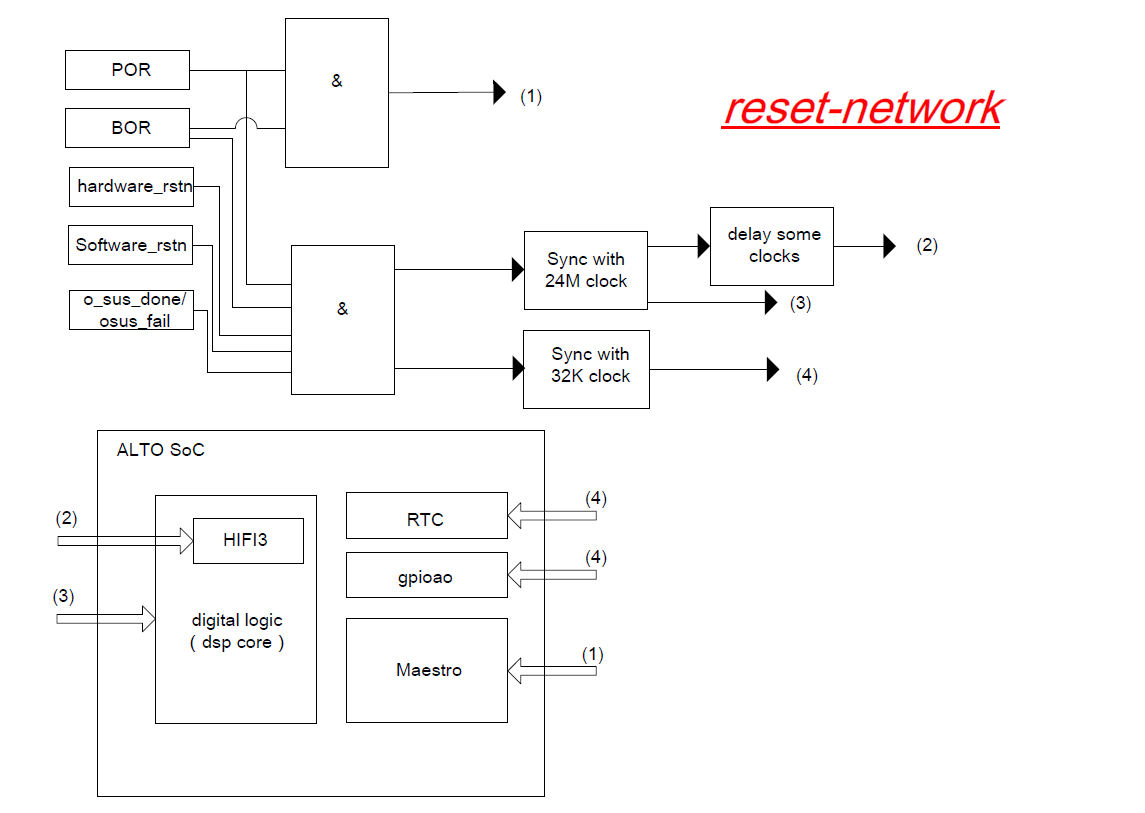

下图显示了复位网络。来自不同功能模块的 4 种复位信号。复位1由POR和BOR产生,其余3种复位信号可能来自POR/BOR、硬件复位、软件复位、o_sus_done或o_sus_fail。

# 音频编解码器

音频编解码器包括以下功能模块:

2路模数转换器(ADC)和附加模拟电路:

2路支持提升增益的单端或差分模拟输入,可用于无电容配置中的线路输入或麦克风输入应用。录音路径支持两级增益:模拟增益为-2dB至+24dB,步进值为2dB,数字可编程增益为-64至+63 dB,步进值为1dB

10路单声道或5路立体声数字麦克风接口,具有可编程DMIC时钟频率

2路数模转换器(DAC)和附加模拟电路:

1个立体声差分无电容耳机和线路输出

2路单声道差分线路输出

内置稳压电源:

1个低噪声线性稳压器,为部分模拟电路供电

2个麦克风偏置输出,可用于最多驱动2个模拟麦克风

信号处理功能:

自动增益/电平控制 (AGC) ,在录制过程中可以自适应声音的音量,维持录音音量在指定范围内

风噪滤波器(WNF),可编程高通滤波功能,可在大风环境或开窗车辆中降低录制期间的风噪声

音频接口自适应同步器(AIAS)系统能够在平均采样频率接近标准化值(最大3%差异)时自动同步输入数据

用于数字麦克风的数字WhisperTrigger,可在检测到语音活动时唤醒芯片

其主要特性包括:

2路24位/192Ksps ADC 和2路24位/192Ksps DAC

低BOM无电容输入和输出

多达10个数字麦克风接口,具有可编程DMIC时钟频率并支持低功耗模式

16至24位有符号线性PCM格式, 支持采样率:8, 11.025, 12, 16, 22.05, 24, 32, 44.1, 48, 88.2, 96, 176.4, 192kHz

嵌入式低噪声线性稳压器,对电源噪声具有高弹性

ADC路径上的低功耗工作模式

降低声音毛刺:

软静音模式

过零增益变化

优化 SNR 的自动增益/电平控制 (AGC)

可编程风噪滤波 (WNF)

DAC从模式,支持AIAS自动数据速率同步

ADC从模式,支持AIAS自动数据速率同步

WhisperTrigger, 数字麦克风的语音活动检测

# 时钟与采样率

# 时钟生成和管理

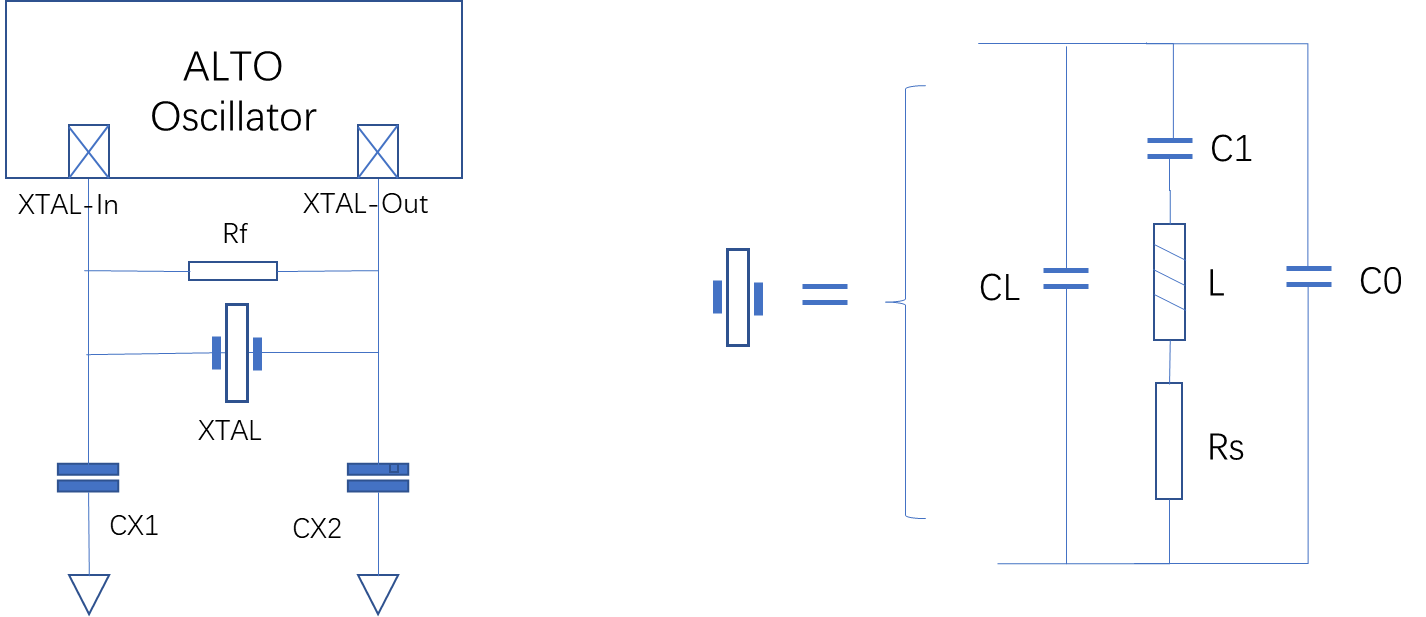

下图为晶体振荡器电路和晶体等效电路。只有晶体 (XTAL) 和电容 CX1 和 CX2 需要在 XTAL-输入和 XTAL-Out 上从外部连接。振荡器还具有旁路模式,外部时钟直接连接到XTAL-In引脚。

为了获得最佳性能,为片上振荡器选择匹配的晶体非常重要。负载电容CL、串联电阻Rs和驱动电平DL是选择晶体时要考虑的重要参数。Rf是晶体开始振荡的反馈电阻。选择合适的晶体后,外部负载电容CX1和CX2的值通常可以通过以下公式计算:

CX1=CX2= CL -- (Cpad + Cparasitic)

其中:

CL:每个端子的晶体负载电容

Cpad: XTAL输入和XTAL输出引脚的焊盘电容

Cparasitic: 外部电路的寄生或杂散电容。

下表列出了晶体振荡器的电气特性:

| Description | Symbol | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Frequency range (crystal mode) | Fref | 24 | MHz | ||

| Frequency range (bypass mode) | Fref | 24 | MHz | ||

| Frequency accuracy | -20 | 20 | ppm | ||

| Cycle-to-cycle Jitter | CCJ | -10 | 10 | ps | |

| Output Duty Cycle | t-do | 40 | 50 | 60 | % |

| Equivalent Series Resistance | 40 | Ω | |||

| CL | 8 | pF | |||

| Rf | 1 | MΩ | |||

| Total Power (unloaded) | IDD | TBD | mA |

# 核心时钟

时钟发生模块包括PLL,可生成到HiFi3内核、编解码器、USB、I2S、SPI和其他接口的时钟。

共有2个参考振荡器。片内32kHz RC振荡器在上电和低功耗模式下使用。24MHz晶体振荡器用于在活动模式下提供参考时钟。

编解码器主时钟为12MHz,USB主时钟为24MHz,系统时钟最高可达200MHz。

时钟要求:

| Clock | Active mode (max MHz) | Sleep mode (MHz) | Duty-cycle |

|---|---|---|---|

| CPU/AHB | 200 | 0 | 45%-55% |

| APB1 | 50 | 0 | 45%-55% |

| APB2 | 100 | 0 | |

| Flash | 108 | 0 | 45%-55% |

| JTAG | External | 0 | 45%-55% |

| Codec | 12 | 0 | 45%-55% |

| USB | 24 | 0 | 45%-55% |

| I2S | 24 | 0 | 45%-55% |

| PLL ref clk | 24 | 0 | 45%-55% |

# 采样率

采样频率和主时钟频率:

| Parameter | Description | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Fs | Sampling frequency in normal mode | 8 | 192 | kHz | |

| Fs | Sampling frequency in low power consumption mode (ADC only) | 8 | 16 | kHz | |

| Fmclk | Main clock frequency | 12 or 13 | MHz | ||

| Dmclk | Main clock duty cycle | 0.45 | 0.5 | 0.55 | - |

MCLK、DMIC_CLK频率和可用 Fs 之间的关系:

| Clock division ratio (DMIC_RATE) | DMIC-CLK: frequency (Fdmic≠clk) for Fmclk=12Mhz | DMIC-CLK: frequency (Fdmic≠clk) for Fmclk=13Mhz | Available Fs (kHz) |

|---|---|---|---|

| 16 | 750 kHz | 812.5 kHz | 8, 11.025, 12, 16 |

| 12 | 1 MHz | 1.08 MHz | 8, 11.025, 12, 16 |

| 5 | 2.4 MHz | 2.6 MHz | 8, 11.025, 12, 16, 22.05, 24, 32, 44.1, 48, 88.2, 96, 176.4, 192 |

| 4 | 3.0 MHz | 3.25 MHz | 8, 11.025, 12, 16, 22.05, 24, 32, 44.1, 48, 88.2, 96, 176.4, 192 |

# PLL

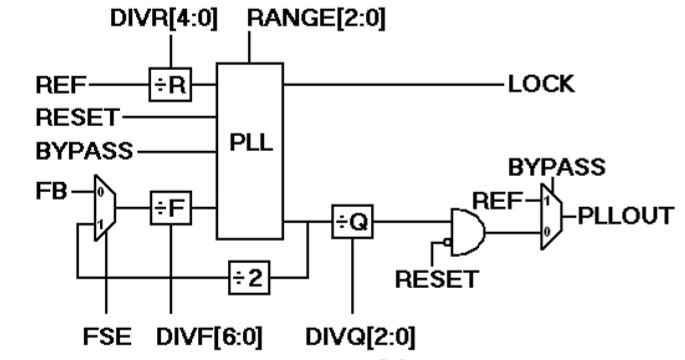

下图显示了PLL架构,其中典型参考时钟为24MHz。

下表列出了PLL操作的信号:

| Signal | Usage | Limitation |

|---|---|---|

| DIVR[4:0] | Reference Divider Value (binary value + 1 : 00000 = ÷1) | Both REF and post-divide REF must be within the specified range |

| DIVF[6:0] | Feedback Divider Value (binary value + 1 : 0000000 = ÷1) | VCO must be within the specified range |

| DIVQ[2:0] | Output Divider Value (2^ binary value) 001 = ÷2 100 = ÷16 010 = ÷4 101 = ÷32 011 = ÷8 110 = ÷64 | |

| FSE | Chooses between internal and external input paths: 0 = FB pin input 1 = internal feedback | |

| RANGE [2:0] | PLL Filter Range 000=BYPASS 100=26-42MHz 001=Reserved 101=42-68MHz 010=10-16MHz 110=68-110MHz 011=16-26MHz 111=110-200MH | This sets the PLL loop filter to work with the post-reference divider frequency. Choose the highest valid range for best jitter performance, or optimize with post-silicon characterization. |

下表列出了PLL关键参数:

| Description | Symbol | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Input Frequency | Fref | 24 | MHz | ||

| VCO Frequency | Fvco | 1000 | 2000 | MHz | |

| Output Frequency | Fout | 20 | 1000 | MHz | |

| Output Duty Cycle | t-do | 45 | 55 | % | |

| Maximum Lock Time | t-lock | 50 | µs | ||

| Reset Time | t-reset | 1 | µs | ||

| Maximum Long Term Jitter | LTJ | ±1% Divided-Ref Period | |||

| Maximum Cycle to Cycle Jitter | CCJ | ±1% Output Period | |||

| Total Power (unloaded) | IDD | 2 | mA | ||

# 控制端口

# USB 端口

SNC8508 提供具有集成 PHY 的全功能 USB 控制器,支持 USB2.0 FS/HS 和 USB 音频类规范 UAC 1.0/2.0。

| Item | Unit | Specification | Comment |

|---|---|---|---|

| USB standard | 2.0 full speed and high speed, device | ||

| VBUS voltage | V | 5.0/3.3 | |

| Interface type | Type-C/Micro USB |

# I2C/UART

| Item | Quantity | Unit | Specification | Comment |

|---|---|---|---|---|

| UART | 1 | bps | Up to 3M | TX and RX |

| I2C | 2 | kbps | Up to 400K |

# I2S端口

有2个 I2S 端口,如下表所示。

| Item | Unit | Specification | Comment |

|---|---|---|---|

| Interface number | 3 I2S interface, with word clock, bit clock, data-in, data-out | ||

| Word clock | kHz | Up to 192 | 8, 16, 32, 44.1, 48, 88.2, 96, 176.4, 192 |

| Data width | bits | 16/20/24 | |

| Format | Standard, left-justified, right-justified |

I2S 引脚是 GPIO 可重复使用的引脚。GPIO 映射如下表所述,其中 CLK 是位时钟,WS 是字时钟,SDI 是输入数据,SDO 是输出数据。

| I2S-1 | I2S-2 | ||

|---|---|---|---|

| I2S1_clk | GPIO0 | I2S2_clk | GPIO4 |

| I2S1_ws | GPIO1 | I2S2_ws | GPIO5 |

| I2S1_sdi | GPIO2 | I2S2_sdi | GPIO6 |

| I2S1_sdo | GPIO3 | I2S2_sdo | GPIO7 |

# 逐次逼近型模数转换器(SAR ADC)

片上2个12位逐次逼近型模数转换器(SAR ADC), 可用于按钮检测、电池监视或其它模拟传感器输入测量。

| Parameters | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|

| Resolution | 12 | Bits | ||

| ENOB | 11 | Bits | ||

| Sampling rate | 5 | Msps | ||

| Channel | TBD | |||

| AVDD-aux-ADC | 3.3 | V | ||

| DVDD-aux-ADC | 1.1 | V | ||

| Input voltage range | 0 | 3.3 | V | |

| INL accuracy | -2 | 2 | LSB | |

| DNL accuracy | -1 | 1 | LSB | |

| Offset | -2 | 2 | LSB | |

| Gain error | -1 | 1 | % | |

| Hardware conversion time | 1 | us |

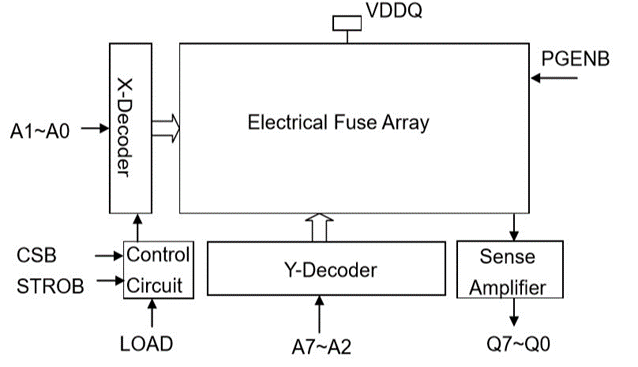

# eFuse

有1个 256 位的 OTP 存储器,它被组织为 32 位乘以 8。这是一次性可编程电熔丝,带有随机访问接口。电熔丝是一种在标准CMOS逻辑工艺中制造的非易失性存储器。

| Pin name | Signal type | Description |

|---|---|---|

| CSB | Input | Active-low chip select in low power standby mode |

| STROBE | Input | High to turn ‘ON’ the array for read or program access |

| LOAD | Input | High to turn ‘ON’ sense amplifier and load data into latch |

| Q7~Q0 | Output | Data output |

| VDDQ | Input | High voltage for fuse programming, ground for read |

| A7~A0 | Input | Address pins |

| PGENB | Input | Program enable (active low) |

| VDD | Supply | Core supply voltage |

| VSS | Supply | Ground |

主要特性:

编程条件:

VDDQ: 2.5V±10%

VDD: 1.1V±10%

温度: 125℃~-40℃

编程时间: 10us±1us

读取条件:

VDDQ: 0V or floating

VDD: 0.81V~1.21V

温度: 125℃~ -40℃

异步信号接口

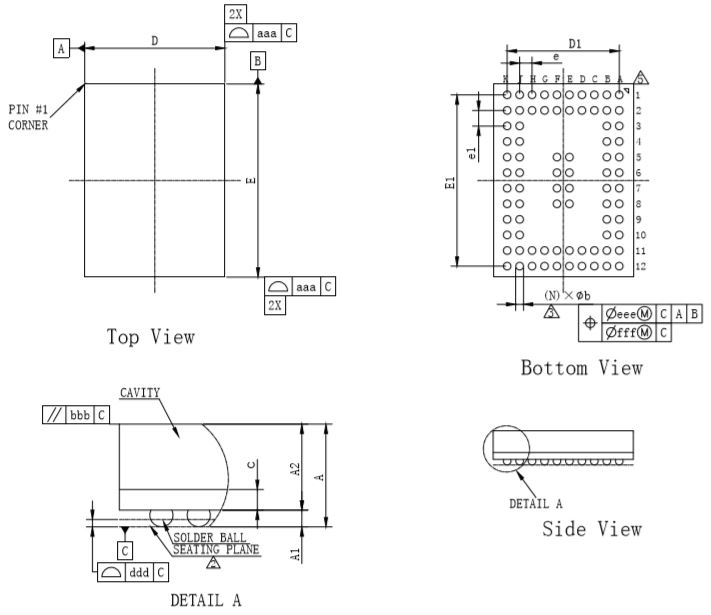

# 尺寸规格

BGA80封装规格信息如下:

# 订购信息

Part Number | Type | Package Size | Packing | MoQ |

|---|---|---|---|---|

| SNC8508 | BGA-80L | 4.5mm*6.2mm*1.2mm X: 0.5mm, Y: 0.4mm Pitch | Tape&Reel | 3K |